Julian M. Kunkel Pavan Balaji Jack Dongarra (Eds.)

# High Performance Computing

31st International Conference, ISC High Performance 2016 Frankfurt, Germany, June 19–23, 2016 Proceedings

# **Lecture Notes in Computer Science**

9697

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

# **Editorial Board**

David Hutchison

Lancaster University, Lancaster, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Zürich, Switzerland

John C. Mitchell

Stanford University, Stanford, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

TU Dortmund University, Dortmund, Germany

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Gerhard Weikum

Max Planck Institute for Informatics, Saarbrücken, Germany

More information about this series at http://www.springer.com/series/7407

Julian M. Kunkel · Pavan Balaji Jack Dongarra (Eds.)

# High Performance Computing

31st International Conference, ISC High Performance 2016 Frankfurt, Germany, June 19–23, 2016 Proceedings

Editors

Julian M. Kunkel

Deutsches Klimarechenzentrum

Hamburg

Germany

Pavan Balaji Argonne National Laboratory Lemont, IL USA Jack Dongarra University of Tennessee Knoxville, TN USA

ISSN 0302-9743 ISSN 1611-3349 (electronic) Lecture Notes in Computer Science ISBN 978-3-319-41320-4 ISBN 978-3-319-41321-1 (eBook) DOI 10.1007/978-3-319-41321-1

Library of Congress Control Number: 2016942512

LNCS Sublibrary: SL1 - Theoretical Computer Science and General Issues

## © Springer International Publishing Switzerland 2016

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

This Springer imprint is published by Springer Nature

The registered company is Springer International Publishing AG Switzerland

# **Preface**

ISC High Performance, formerly known as the International Supercomputing Conference, was founded in 1986 as the Supercomputer Seminar. Originally organized by Hans Meuer, Professor of Computer Science at the University of Mannheim and former director of the computer center, the seminar brought together a group of 81 scientists and industrial partners who all shared an interest in high-performance computing. Since then the annual conference has become a major international event within the HPC community, and accompanying its growth in size over the years, the conference has moved from Mannheim via Heidelberg, Dresden, Hamburg, and Leipzig to Frankfurt. With 2,846 attendees and 153 exhibitors from over 56 countries in 2015, we were happy to see that this steady growth of interest also turned ISC High Performance 2016 into a powerful and memorable event.

In 2007, we decided to strengthen the scientific part of the conference by presenting selected talks on relevant research results within the HPC field. These research paper sessions began as a separate day preceding the conference, where slides and accompanying papers were made available via the conference website. The research paper sessions have since evolved into an integral part of the conference, and this year the scientific presentations took place over a period of three days.

For the past several years, the ISC High Performance conference has presented an ISC-sponsored award to encourage outstanding research in high-performance computing and to honor the overall best research paper submitted to the conference. Last year, this annual award was renamed as the Hans Meuer Award in memory of the late Dr. Hans Meuer, general chair of the ISC conference from 1986 through 2014, and cofounder of the TOP500 project. From all research papers submitted, the Research Papers Program Committee nominated the three papers with the highest review scores for the award and, in a face-to-face meeting, elected the best paper.

For ISC High Performance 2016, the call for participation was issued in Fall 2015, inviting researchers and developers to submit the latest results of their work to the Program Committee. In all, 60 papers were submitted from authors all over the world. This year, again a significant effort was made to improve the overall process. The Research Papers Program Committee consisted of 54 members selected from several countries throughout the world. Furthermore, 17 external expert reviewers were invited from the community to help with paper reviews of specific topics. After initial reviews were in place, a rebuttal process was made in which authors were given an opportunity to respond to reviewers' questions and help clarify issues the reviewers might have. To come to a final consensus on the papers to be accepted, we introduced a face-to-face meeting where each paper was discussed. Finally, the committee selected 25 papers for publication and for presentation in the research paper sessions.

#### VI Preface

We are pleased to announce that many fascinating topics in HPC are covered by the proceedings. The papers address the following issues in regards to the development of an environment for exascale supercomputers:

- Cost-efficient data centers

- Scalable applications

- Advancements in algorithms

- Scientific libraries

- Programming models

- Architectures

- Performance models and analysis

- Automatic performance optimization

- Parallel I/O

- Energy efficiency

We believe that this selection is highly appealing across a number of specializations. Three award committees selected papers considered to be of exceptional quality and worthy of special recognition:

- The Hans Meuer Award honors the overall best research paper submitted to the conference. The award went to:

- "Mitigating MPI Message Matching Misery" by Mario Flajslik, James Dinan, and Keith D. Underwood.

- PRACE, the Partnership for Advanced Computing in Europe, awards a prize to the best scientific paper by a European student or scientist. This year's award was granted to:

- "Dynamic Sparse-Matrix Allocation on GPUs" by James King, Thomas Gilray, Robert M. Kirby and Matthew Might.

- The Gauss Centre for Supercomputing sponsors the Gauss Award. This award is assigned to the most outstanding paper in the field of scalable supercomputing and went to:

- "Predictive Modeling for Job Power Consumption in HPC Systems" by Andrea Borghesi, Andrea Bartolini, Michele Lombardi, Michela Milano and Luca Benin.

We would like to express our gratitude to all our colleagues for submitting papers to the ISC scientific sessions, as well as to the members of the Program Committee for organizing this year's attractive program.

June 2016

Julian M. Kunkel Pavan Balaji Jack Dongarra

# **Organization**

# **Research Papers Program Committee**

David Abramson Monash University, Australia

Ilkay Altintas San Diego Supercomputer Center, USA

Pavan Balaji Argonne National Laboratory, USA (Co-chair)

Thomas Bönisch High Performance Computing Center Stuttgart, Germany

Mahdi Bohlouli

Ron Brightwell

Eva Burrows

Xing Cai

Ewa Deelman

University of Siegen, Germany

Sandia National Laboratories, USA

University of Bergen, Norway

Simula Research Laboratory, Norway

USC Information Sciences Institute, USA

Jack Dongarra University of Tennessee and Oak Ridge National

Laboratory, USA (Chair)

Tomas Flouri Heidelberg Institute for Theoretical Studies, Germany

Holger Fröning University of Heidelberg, Germany

Lutz Gross University of Queensland, Australia

Daniel Hackenberg Technische Universität Dresden, Germany

Bilel Hadri KAUST Supercomputing Lab, Saudi Arabia

Mary Hall University of Utah, USA

David Ham Imperial College London, UK

Frank Hannig Friedrich-Alexander-Universität Erlangen-Nürnberg,

Germany

Magne Haveraaen University of Bergen, Norway

Stephan Herhut Google, Denmark

Weicheng Huang National Center for High-Performance Computing, Taiwan

Zhiyi Huang University of Otago, New Zealand

Volodymyr Kindratenko University of Illinois at Urbana-Champaign, USA

Julian M. Kunkel Deutsches Klimarechenzentrum, Germany

(Proceedings Chair)

Dong Li University of California, Merced, USA

Fang-Pang Lin National Center for High-Performance Computing, Taiwan

Qing Liu Oak Ridge National Laboratory, USA

Hatem Ltaief KAUST, Saudi Arabia

Thomas Ludwig Deutsches Klimarechenzentrum, Germany Arthur Maccabe Oak Ridge National Laboratory, USA

M. Manjunathaiah University of Reading, UK Simon Mcintosh-Smith University of Bristol, UK

Richard Membarth DFKI and Saarland University, Germany

Marek Michalewicz A\*Star Computational Resource Center, Singapore

#### VIII Organization

Bernd Mohr Jülich Supercomputing Center, Germany

Alexander Moskovsky RSC SCKIF, Russia

Matthias Müller RWTH Aachen University, Germany

Kengo Nakajima University of Tokyo, Japan Julio Ortega Universidad de Granada, Spain Dhabaleswar Panda Ohio State University, USA

Huynh Phung A\*STAR, Singapore Thomas Poulet CSIRO, Australia

Ying Qian East China Normal University, China Francisco Rodrigo Universidad Carlos III de Madrid, Spain

Sven-Bodo Scholz Heriot-Watt University, UK

Federico Silla Technical University of Valencia, Spain

Yogesh Simmhan Indian Institute of Science, India

Alexandros Stamatakis Technische Universität München, Germany

Osamu Tatebe University of Tsukuba, Japan Michela Taufer University of Delaware, USA Jeyan Thiyagalingam University of Liverpool, UK

Yuichi Tsujita RIKEN AICS, Japan

Jeff Vetter Oak Ridge National Laboratory, USA

Xavier Vigouroux Bull, France

Vladimir Voevodin Lomonosov Moscow State University, Russia Thomas Wild Technische Universität München, Germany

Peter Ziegenhein Institute of Cancer Research, UK

# **PHD Forum Program Committee**

Lorena Barba George Washington University, USA (Chair)

Anshu Dubey Argonne National Laboratory, USA

Anne Elster Norwegian University of Science and Technology,

Norway

Fernanda Foerter Oak Ridge National Laboratory, USA

Georg Hager Friedrich-Alexander-Universität Erlangen-Nürnberg,

Germany

Paul Kelly Imperial College London, UK

Kengo Nakajima University of Tokyo, Japan

Amanda Randles Duke University, USA

Michelle Mills Strout University of Arizona, USA

Ana Lucia Varbanescu University of Amsterdam, The Netherlands

Michela Taufer University of Delaware, USA

Richard Vuduc Georgia Institute of Technology, USA

Gerhard Wellein Friedrich-Alexander-Universität Erlangen-Nürnberg,

Germany (Co-chair)

Felix Wolf Technische Universität Darmstadt, Germany

Rio Yokota Tokyo Institute of Technology, Japan

# **Research Poster Session Program Committee**

Alvaro Aguilera ZIH/TU Dresden, Germany Mahdi Bohlouli University of Siegen, Germany

Thomas Bönisch HLRS, Germany

Xing Cai Simula Research Laboratory, Norway Javier Garcia Blas Universidad Carlos III de Madrid, Spain

David Ham Imperial College London, UK

Khalid Hasanov IBM Research, Ireland

Weicheng Huang National Center for High-Performance Computing, Taiwan

Julian Kunkel Deutsches Klimarechenzentrum, Germany Ravindranath Reddy UCD School of Computer Science, Ireland

Manumachu

Simon McIntosh-Smith University of Bristol, UK

Germany

Kengo Nakajima University of Tokyo, Japan

Gabriel Noaje A\*STAR Computational Resource Centre, Singapore

Julio Ortega University of Granada, Spain

Andrej Sozykin Ural Federal University, Russia

Osamu Tatebe University of Tsukuba, Japan

Jeyarajan Oxford University, UK

Thiyagalingam

Vladimir Voevodin

Peter Ziegenhein

Moscow State University, Russia (Chair)

The Institute of Cancer Research, UK

# **HPC in Asia Program Committee**

Taisuke Boku University of Tsukuba, Japan (Chair)

Ralph Bording Pawsey, Australia Horst Gietl ISC Group, Germany

R. Govindarjan

Weicheng Huang

Zhong Jin

Jysoo Lee

Yutong Lu

RISC, India

NCHC, Taiwan

CAS, China

KISTI, Korea

NUDT, China

Martin Meuer ISC Group, Germany

Marek T. Michalewicz A\*STAR, Singapore

Hiroshi Nakashima Kyoto University, Japan

Nages Sieslack ISC Group, Germany

# **Tutorials Committee**

Pavan Balaji Argonne National Laboratory, USA

Rosa M. Badia BSC, Spain

#### X Organization

Franck Cappello INRIA and UIUC, France

James Dinan Intel, USA

Ganesh Gopalakrishnan University of Utah, USA

Bill Gropp University of Illinois at Urbana-Champaign, USA (Chair)

Torsten Hoefler ETH Zurich, Switzerland University of Colorado, USA

Fred Johnson SAIC, USA

Alice Koniges LBNL, USA

Michael Resch HLRS, Germany

Rajeev Thakur Argonne National Laboratory, USA

## **BoFs Committee**

David Bader Georgia Institute of Technology, USA

Natalie Bates Energy Efficient HPC Working Group, USA

Costas Bekas IBM Research Zurich, Switzerland

Alfred Geiger T-Systems Solutions for Research, Germany

Horst Gietl ISC Group, Germany (Chair)

Georg Hager Friedrich-Alexander-Universität Erlangen-Nürnberg,

Germany

Peter Kogge University of Notre Dame, USA

Julian Kunkel Deutsches Klimarechenzentrum, Germany

Jysoo Lee KISTI, Korea

Pekka Lehtovuori CSC – IT Center for Science, Finland Cynthia R. McIntyre Washington Technology Partners, USA

Marek Michalewicz A\*STAR Computational Resource Center, Singapore

Bernd Mohr Jülich Supercomputing Center, Germany

Jean-Philippe Nominé CEA, France Marie-Christine Sawley Intel, France

Martin Schulz Lawrence Livermore National Laboratory, USA Rainer Spurzem Chinese Academy of Sciences and University

of Heidelberg, Germany

Vladimir Voevodin Moscow State University, Russia

Heike Walther ISC Group, Germany

Michele Weiland EPCC - The University of Edinburgh, UK

Gerhard Wellein Friedrich-Alexander-Universität Erlangen-Nürnberg,

Germany

Jan Wender science+computing, Germany

Andreas Wierse SICOS BW, Germany

# **Workshop Committee**

Rosa M. Badia BSC, Spain Francois Bodin Irisa, France Bronis R. de Supinski LLNL, USA Craig Lucas NAG, UK Gerald F. Lofstead II SNL, USA

Naoya Maruyama RIKEN AICS, Japan Bernd Mohr JSC, Germany (Co-chair)

Marie-Christine Sawley Intel, France

Seetharami R. Seelam IBM Research, USA

John Shalf NERC, USA

Michela Taufer University of Delaware, USA (Co-chair)

Antonino Tumeo PNNL, USA

# **Additional Reviewers for the Research Papers**

Cihan Altinay The University of Queensland, Australia

Lucas Czech Heidelberg Institute for Theoretical Studies, Germany

Minh Dinh University of Queensland, Australia

Tingxing Dong AMD, USA

Joel Fenwick University of Queensland, Australia

Yuhua Guo Virginia Commonwealth University, USA

Dan Huang University of Central Florida, USA

Siddhartha Jana University of Houston, USA

Chao Jin University of Queensland, Australia

Hideyuki Kawashima University of Tsukuba, Japan

Jialin Liu Lawrence Berkeley National Lab, USA Sarah Lutteropp Karlsruhe Institute of Technology, Germany

Radhika Nath Reading University, UK

Hoang Nguyen University of Queensland, Australia

Milos Puzovic STFC, Hartree, UK

Joseph Schuchart TU Dresden, Germany

Huadong Xia MicroStrategy, USA

# **Contents**

| Autotuning and Thread Mapping                                                                                                    |     |

|----------------------------------------------------------------------------------------------------------------------------------|-----|

| An Analytical Model-Based Auto-tuning Framework for Locality-Aware Loop Scheduling                                               | 3   |

| Performance, Design, and Autotuning of Batched GEMM for GPUs Ahmad Abdelfattah, Azzam Haidar, Stanimire Tomov, and Jack Dongarra | 21  |

| TCU: A Multi-Objective Hardware Thread Mapping Unit for HPC Clusters Ravi Kumar Pujari, Thomas Wild, and Andreas Herkersdorf     | 39  |

| Data Locality and Decomposition                                                                                                  |     |

| Dynamic Sparse-Matrix Allocation on GPUs                                                                                         | 61  |

| An Efficient Parallel Load-Balancing Framework for Orthogonal Decomposition of Geometrical Data                                  | 81  |

| Parallel Community Detection Algorithm Using a Data Partitioning Strategy with Pairwise Subdomain Duplication                    | 98  |

| TiDA: High-Level Programming Abstractions for Data  Locality Management                                                          | 116 |

| Scalable Applications                                                                                                            |     |

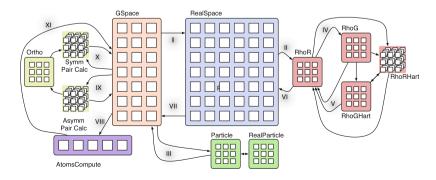

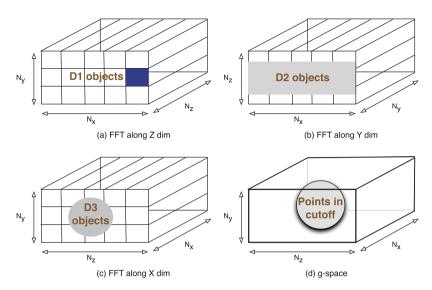

| OpenAtom: Scalable Ab-Initio Molecular Dynamics with Diverse Capabilities                                                        | 139 |

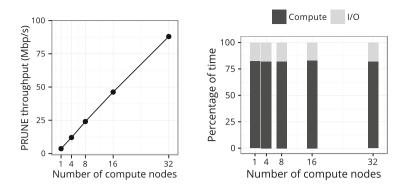

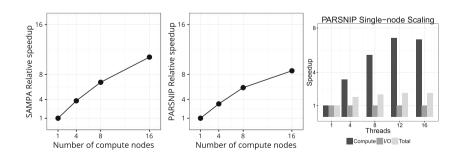

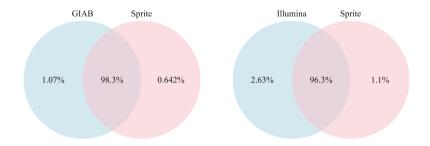

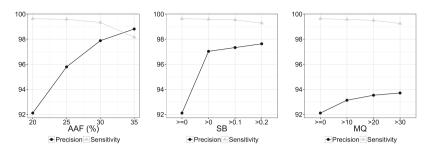

| SPRITE: A Fast Parallel SNP Detection Pipeline                                                                                                                                                       | 159 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Machine Learning                                                                                                                                                                                     |     |

| Predictive Modeling for Job Power Consumption in HPC Systems                                                                                                                                         | 181 |

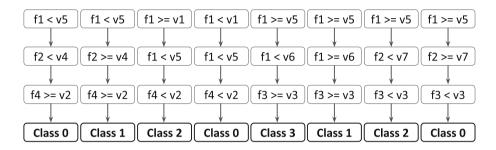

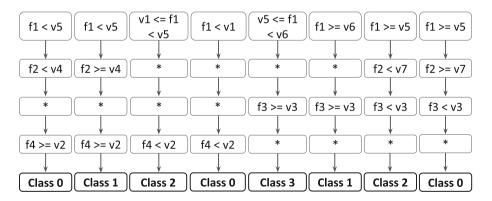

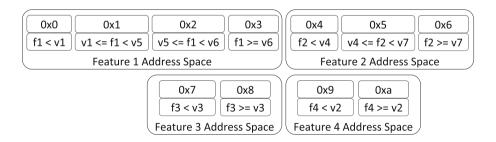

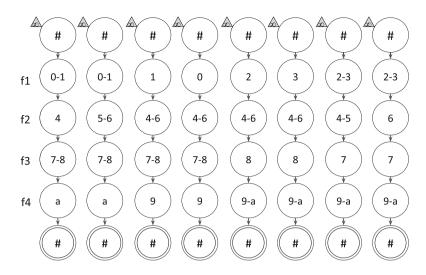

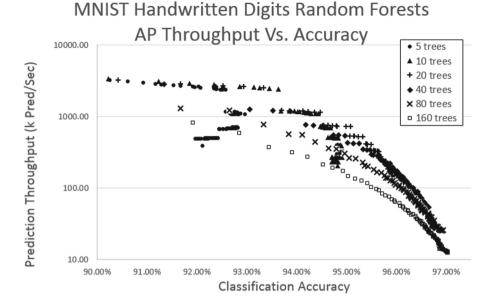

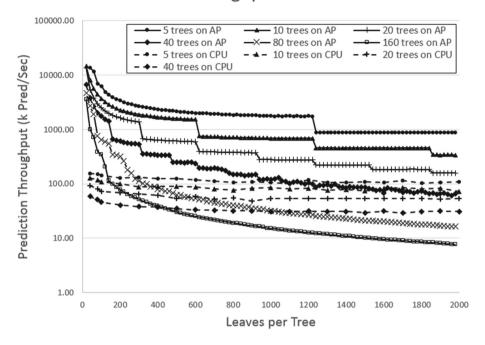

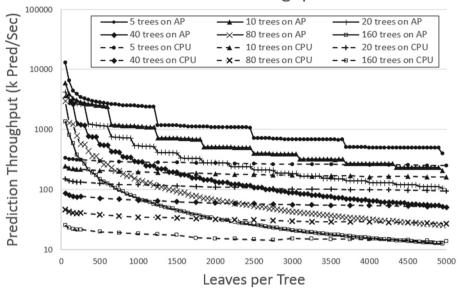

| Towards Machine Learning on the Automata Processor                                                                                                                                                   | 200 |

| AutoMOMML: Automatic Multi-objective Modeling with Machine Learning                                                                                                                                  | 219 |

| Datacenters and Cloud                                                                                                                                                                                |     |

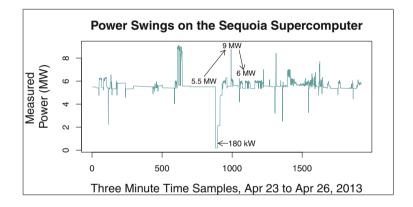

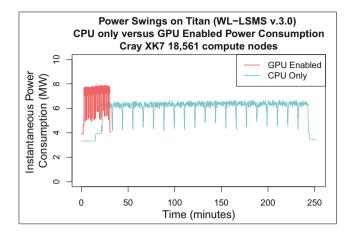

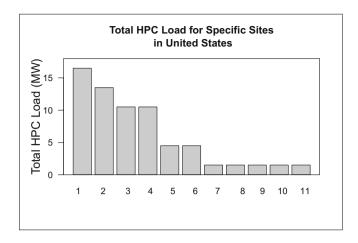

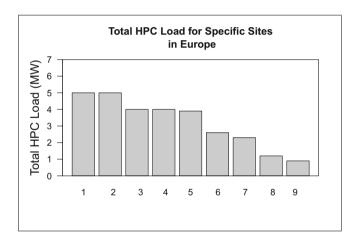

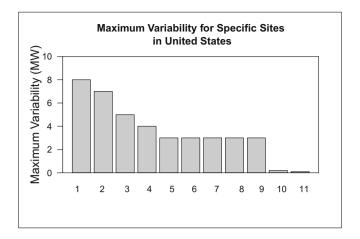

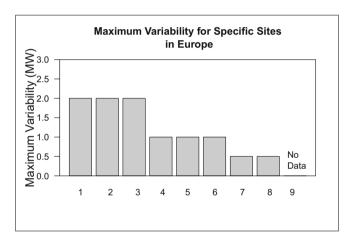

| Supercomputing Centers and Electricity Service Providers:  A Geographically Distributed Perspective on Demand Management in Europe and the United States                                             | 243 |

| Sonja Klingert, Ghaleb Abdulla, and Mehdi Sheikhalishahi                                                                                                                                             |     |

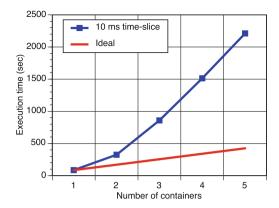

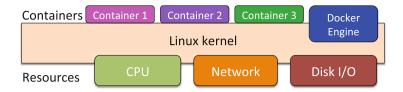

| Resource Management for Running HPC Applications in Container Clouds Stephen Herbein, Ayush Dusia, Aaron Landwehr, Sean McDaniel, Jose Monsalve, Yang Yang, Seetharami R. Seelam, and Michela Taufer | 261 |

| Communication Runtime                                                                                                                                                                                |     |

| Mitigating MPI Message Matching Misery                                                                                                                                                               | 281 |

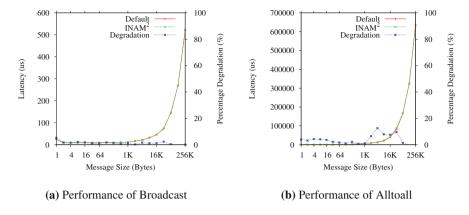

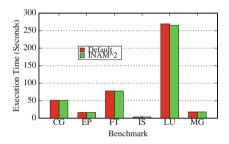

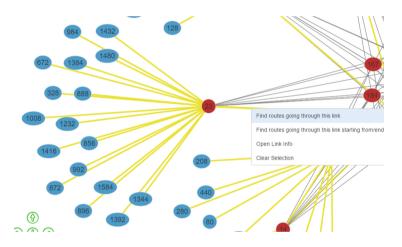

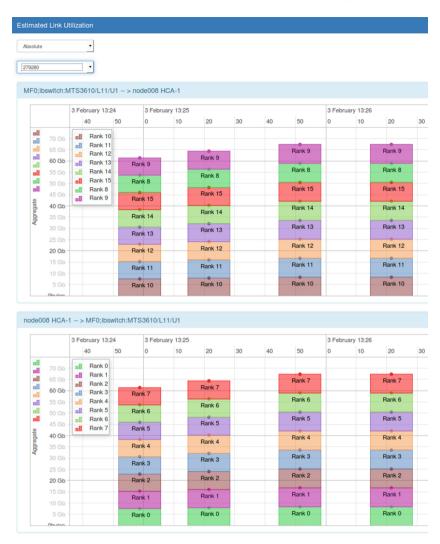

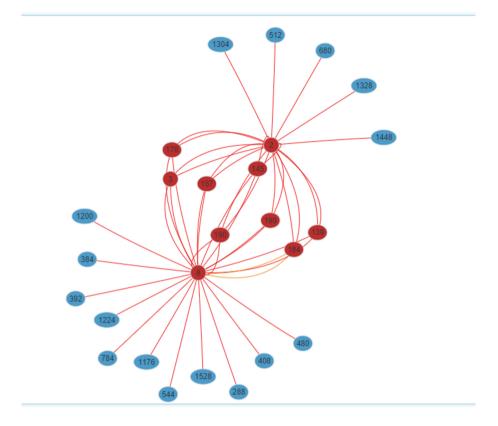

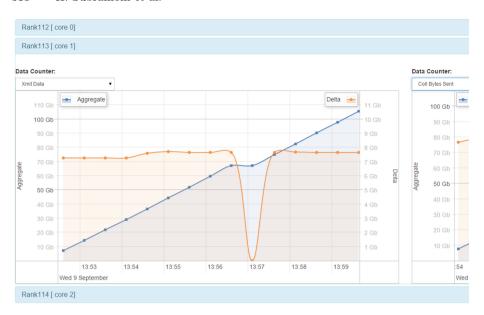

| INAM <sup>2</sup> : InfiniBand Network Analysis and Monitoring with MPI                                                                                                                              | 300 |

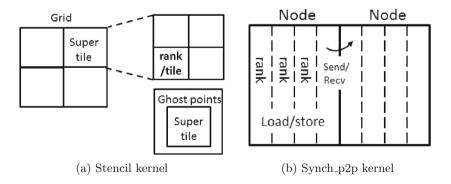

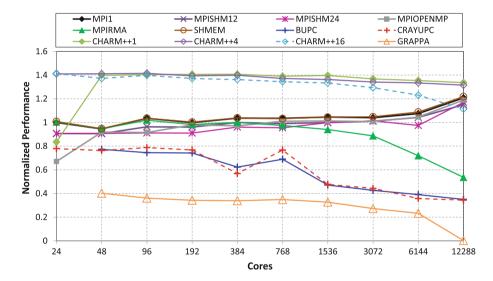

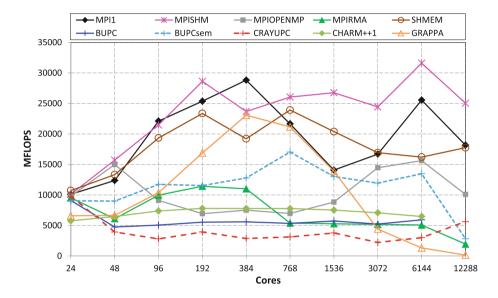

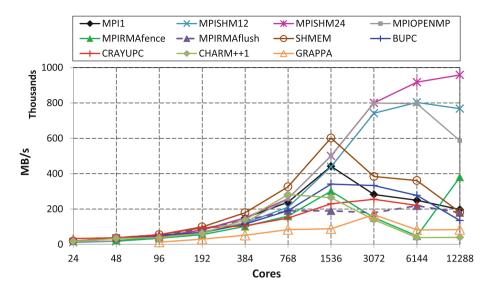

| Comparing Runtime Systems with Exascale Ambitions Using the Parallel Research Kernels                                                                                                                | 321 |

| Intel Xeon Phi                                                                                                                                                                                                             |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

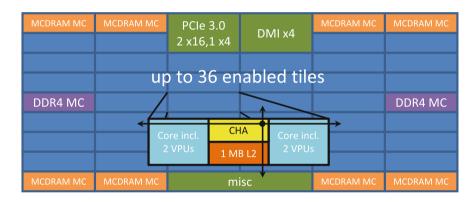

| High Order Seismic Simulations on the Intel Xeon Phi Processor (Knights Landing)                                                                                                                                           | 343 |

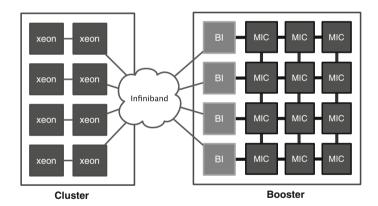

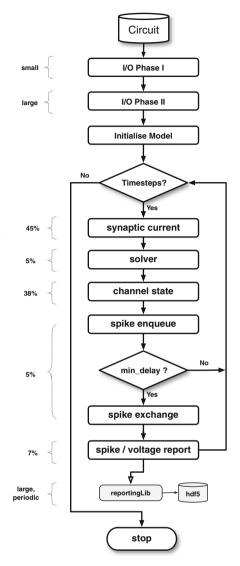

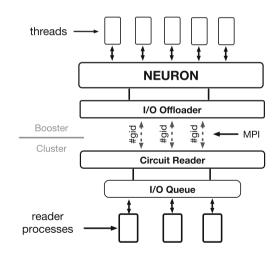

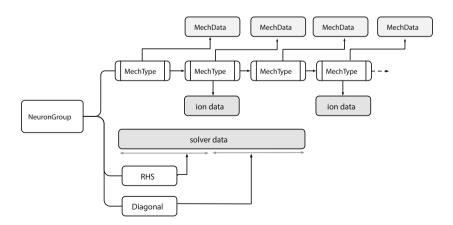

| Leveraging a Cluster-Booster Architecture for Brain-Scale Simulations<br>Pramod Kumbhar, Michael Hines, Aleksandr Ovcharenko,<br>Damian A. Mallon, James King, Florentino Sainz, Felix Schürmann,<br>and Fabien Delalondre | 363 |

| Manycore Architectures                                                                                                                                                                                                     |     |

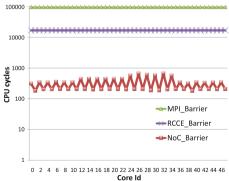

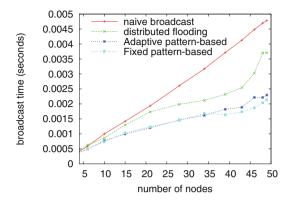

| Efficient and Predictable Group Communication for Manycore NoCs Karthik Yagna, Onkar Patil, and Frank Mueller                                                                                                              | 383 |

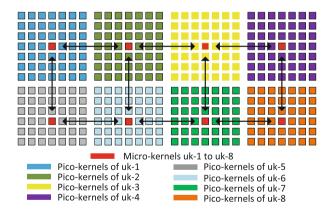

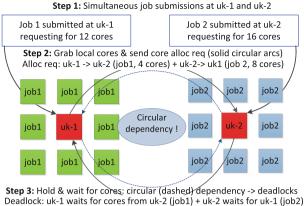

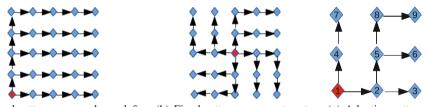

| Distributed Job Allocation for Large-Scale Manycores                                                                                                                                                                       | 404 |

| Extreme-Scale Computations                                                                                                                                                                                                 |     |

| Many-Core Acceleration of a Discrete Ordinates Transport Mini-App at Extreme Scale                                                                                                                                         | 429 |

| Efficiency of High Order Spectral Element Methods on Petascale Architectures                                                                                                                                               | 449 |

| Resilience                                                                                                                                                                                                                 |     |

| Scalability of Partial Differential Equations Preconditioner Resilient to Soft and Hard Faults                                                                                                                             | 469 |

| Multi-versioning Performance Opportunities in BGAS System for Resilience                                                                                                                                                   | 486 |

| Author Index                                                                                                                                                                                                               | 505 |

# An Analytical Model-Based Auto-tuning Framework for Locality-Aware Loop Scheduling

Rengan  $Xu^{1(\boxtimes)}$ , Sunita Chandrasekaran<sup>2</sup>, Xiaonan Tian<sup>1</sup>, and Barbara Chapman<sup>1</sup>

Department of Computer Science, University of Houston, Houston, TX, USA {rxu6,xtian2,bchapman}@uh.edu

Department of Computer and Information Sciences, University of Delaware, Newark, DE, USA schandra@udel.edu

**Abstract.** HPC developers aim to deliver the very best performance. To do so they constantly think about memory bandwidth, memory hierarchy, locality, floating point performance, power/energy constraints and so on. On the other hand, application scientists aim to write performance portable code while exploiting the rich feature set of the hardware. By providing adequate hints to the compilers in the form of directives appropriate executable code is generated. There are tremendous benefits from using directive-based programming. However, applications are also becoming more and more complex and we need sophisticated tools such as auto-tuning to better explore the optimization space. In applications, loops typically form a major and time-consuming portion of the code. Scheduling these loops involves mapping from the loop iteration space to the underlying platform - for example GPU threads. The user tries different scheduling techniques until the best one is identified. However, this process can be quite tedious and time consuming especially when it is a relatively large application, as the user needs to record the performance of every schedule's run. This paper aims to offer a better solution by proposing an auto-tuning framework that adopts an analytical model guiding the compiler and the runtime to choose an appropriate schedule for the loops, automatically and determining the launch configuration for each of the loop schedules. Our experiments show that the predicted loop schedule by our framework achieves the speedup of 1.29x on an average against the default loop schedule chosen by the compiler.

# 1 Introduction

Heterogeneous architectures that comprise of CPU processors and computational accelerators such as GPUs have been increasingly adopted for scientific computing. The low-level programming models CUDA and OpenCL for GPUs offer users programming interfaces with execution models closely matching that of GPU architectures. Effectively using these interfaces for creating highly optimized applications require programmers to thoroughly understand the underlying architecture, as well as significantly change the program structures and algorithms.

© Springer International Publishing Switzerland 2016 J.M. Kunkel et al. (Eds.): ISC High Performance 2016, LNCS 9697, pp. 3–20, 2016. DOI: 10.1007/978-3-319-41321-1-1

This affects both productivity and performance. Standardized directive-based models such as OpenACC [3] and OpenMP for accelerators [5] require developers to insert directives and runtime calls into the existing source code offloading portions of Fortran or C/C++ codes to be executed on accelerators.

Directives are high-level language constructs that programmers can use to provide useful hints to compilers to perform certain transformations and optimizations on the annotated code region. The use of directives can significantly improve programming productivity. Users can still achieve high performance of their program comparable to code written in CUDA or OpenCL, subjected to the requirements that a 'careful' choice of directives and compiler optimization strategies be made. One such scenario encountered quite commonly in a program is loop scheduling.

Loop scheduling defines the mapping of loop nest(s) to the underlying architecture. Consider the architecture is a GPU that consists of a number of GPU threads with complex topology settings; it is a daunting task to determine mapping strategies of the loop nest to those threads in order to achieve better performance. Different loop schedules reflect different memory access orders. Loop transformations change memory access orders that results in exploiting better locality - temporal and spatial. The reuse distance model [4] is a classic model predominantly used for CPUs to capture both types of locality in CPU architectures. However we cannot apply this model directly on GPUs due to the significant architectural differences between the CPUs and the GPUs. This paper aims to extend the reuse model to suit its applicability for GPUs.

The main contributions of this paper include:

- To the best of our knowledge, we are the first to propose a locality-aware auto-tuning framework to address the GPU loop scheduling issue.

- In the proposed framework, we extend the classic reuse distance model to GPU architecture in order to estimate GPU cache hit rate accurately.

- Our results demonstrate that our proposed framework chooses the loop schedule producing better performance compared to the default loop schedule chosen by default by the compiler.

The organization of this paper is as follows: Sect. 2 gives an overview of GPU architecture and OpenACC model. Section 3 provides a motivating example illustrating the performance impact of different loop schedules. In Sect. 4, we explain in detail the proposed auto-tuning framework on how to choose a loop schedule with better locality. Performance results are discussed in Sect. 5. Section 6 highlights the related work in this area. We conclude our work in Sect. 7.

# 2 GPU Architecture and OpenACC Directives

GPU architectures differ significantly from that of traditional processors. Employing a Single Instruction Multiple Threads (SIMT) architecture, NVIDIA GPUs have hundreds of cores that can process thousands of software threads simultaneously. GPUs organize both hardware cores and software threads into

two-level of parallelism. Hardware cores are organized into an array of Streaming Multiprocessors (SMs), each SM consisting of a number of cores named as Scalar Processors (SPs). Each SM has its own L1 cache which is not cache coherent, and all SMs share an unified L2 cache.

The compute-intensive part of an application, called kernel, is offloaded to GPUs for parallel execution. The GPU launches massive threads to execute that kernel. The thread unit in GPU scheduling is called a warp (a warp size has 32 threads for NVIDIA GPUs). Multiple warps form a thread block and multiple thread blocks form a grid. Both the thread block and grid can be 1D, 2D, or 3D. For programmers, the challenge to efficiently utilize the massive parallel capabilities of GPUs is to map the kernels to the thread hierarchy, and efficient data layout in the GPU memory hierarchy to maximize coalesced memory access for the threads.

Directive-based high-level programming models for accelerators, e.g. OpenACC and OpenMP extensions for accelerators, have been designed to address the programmability challenge of GPUs. Using these programming models, programmers insert compiler directives into a program to annotate portions of code to be offloaded onto accelerators for executions. This approach relies heavily on the compiler to generate efficient code for thread mapping and data layout. It could be potentially challenging to extract the optimal performance using such an approach rather than using other explicit programming models. However, the directive-based models simplify programming on heterogeneous systems thus saving development time, while also preserving the original code structure assisting in code portability.

OpenACC allows users to specify three levels of parallelism in a data parallel region: gang, worker and vector parallelism to map the loop nests to the multiple-level thread hierarchy of GPUs. Programmer provides hints to map these three-level parallelism to GPU threads but the effectiveness of the mapping relies on the compiler and runtime implementation strategies. We use a high quality, open-source, validated OpenACC compiler called OpenUH [18]. Adhering to OpenACC standards, this compiler maps "gang" to thread block, "worker" to Y-dimension of thread block and "vector" to X-dimension of thread block [3].

# 3 A Motivating Example

Matrix multiplication has been widely used in scientific computing. We use this application to illustrate the importance of loop scheduling in GPU. The square-matrix multiplication we used is C = AB where the size of matrix A, B, and C is  $n \times n$ . The elements in matrix C are  $C_{i,j} = \sum_{k=1}^{n} a_{i,k} b_{k,j}$  where both the indices i and j loops from 1 through n. A double nested loop was constructed to solve this matrix multiplication. Multiple ways could be adopted to map this loop nest to the underlying GPU threads using directive-based programming model. Table 1 shows how this loop nest could be mapped in so many different ways to GPU threads. The table also indicates different launch configurations. The launch configuration specifies the thread block and grid shape and size that are used to

| Loop schedule number | Loop schedule detail      | Performance (ms) |

|----------------------|---------------------------|------------------|

| 0                    | bx(1)/tx(128)             | 3.24             |

| 1                    | by(1)/bx(1) tx(128)       | 3.36             |

| 2                    | by(1) ty(128)/bx(1) tx(1) | 11.04            |

| 3                    | by(1) ty(64)/bx(1) tx(2)  | 5.87             |

| 4                    | by(1) ty(32)/bx(1) tx(4)  | 4.28             |

| 5                    | by(1) ty(16)/bx(1) tx(8)  | 3.47             |

| 6                    | by(1) ty(8)/bx(1) tx(16)  | 3.09             |

| 7                    | by(1) ty(4)/bx(1) tx(32)  | 3.16             |

| 8                    | by(1) ty(2)/bx(1) tx(64)  | 3.19             |

| 9                    | by(1) ty(1)/bx(1) tx(128) | 3.28             |

**Table 1.** The performance difference for matrix multiplication with different loop schedules and launch configurations

run a loop. All of the 10 loop schedules in the table use only one thread block with 128 threads. However, since the loop nest is mapped to threads differently, there are differences in their performance. The loop schedule 0 is the default loop schedule chosen by the compiler. However, we notice that there are other loop schedules demonstrating better performance than the default schedule that the compiler chose. What are the strategies to choose an optimal or sub-optimal loop schedule and its corresponding launch configuration? Our proposed auto-tuning framework discussed in the rest of the paper provides suitable proven answers to this question.

We would like to keep the notations used for our framework as general as possible and not tie it to any specific programming model/language:

- bx, by and bz: denote X, Y and Z dimension of the grid, respectively

- tx, ty and tz: denote X, Y and Z dimension of the thread block, respectively

- num\_bx, num\_by and num\_bz: denote the size of X, Y and Z dimension of the grid, respectively

- num\_tx, num\_ty and num\_tz: denote the size of X, Y and Z dimension of the thread block, respectively

# 4 Auto-tuning for GPU Loop Scheduling

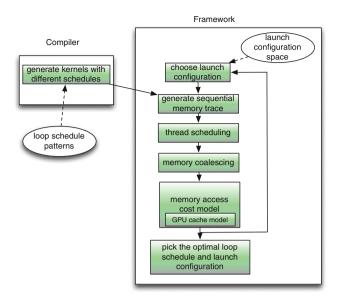

# 4.1 The Auto-tuning Framework

In this section, we describe our auto-tuning framework and the analytical model proposed that enables the identification of the appropriate loop schedule, and the launch configuration used for each of the loop schedules. Figure 1 gives an overview of the auto-tuning framework. The compiler generates multiple kernel files with different loop schedules. The loop schedule is chosen from a set of

Fig. 1. The framework of auto-tuning for loop scheduling

loop schedule patterns which covers both double and triple nested loops. The framework chooses a launch configuration from the launch configuration search space which depends on the iteration space of each loop. The search of launch configuration is guided by the rule of maximizing the GPU occupancy. Before applying the framework, an application needs to run once on CPU to generate a sequential memory trace. Based on the loop schedule and the launch configuration, all memory accesses in the memory trace are assigned to GPU threads. This step defines the access of memory references for GPU threads. Next, the thread scheduling defines the execution order of the memory accesses in the trace.

In the execution of memory accesses, the memory coalescing is very critical. In GPU, a warp (the smallest execution unit) defines a set of consecutive threads. If consecutive threads access consecutive memory addresses, then the memory accesses are coalesced meaning they are merged into fewer memory transactions. We simulate the memory coalescing behavior in GPU architecture in our model. For instance, if the memory addresses referenced by all threads in a warp are in one cache line, then these memory access requests will be merged into only one memory request.

After memory requests are coalesced, the memory trace is fed into the memory access cost model where a memory access cost is computed, with the cache model. This process is repeated until the framework iterates over all loop schedules and the launch configuration space. Finally, the framework picks the optimal loop schedule and the corresponding launch configuration that has the minimal memory access cost. The compiler then recompiles the same program using the selected loop schedule. The major components in this framework will be discussed in the following sub-sections:

# 4.2 Loop Schedule Patterns

We only consider double and triple nested loops. Note that here the loop nest level means parallelizable loop nest. For instance, in the body of the parallelizable loop nest, there could be another nested loop that is sequentially executed. In the current GPU programming models such as OpenACC, the maximum level of the parallelizable loop nest is three. If a nested loop has more levels to parallelize, it can be collapsed into double or triple nested loop.

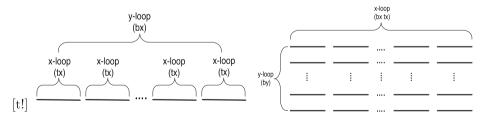

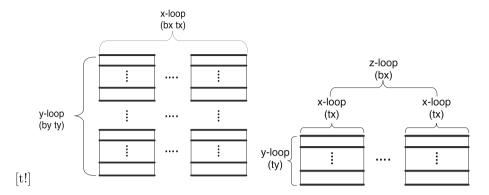

Listing 1.1 shows a double nested loop example. Using the notations described in the previous Sect. 3, we now introduce three loop schedules for the double nested loop (use x-loop for the inner loop and y-loop for the outer loop):

- schedule 2\_1: x-loop is mapped to the X-dimension of a thread block, and y-loop is mapped to the X-dimension of the grid.

- schedule 2.2: x-loop is mapped to X-dimension of both thread block and grid, and y-loop is mapped to Y-dimension of the grid.

- schedule 2-3: x-loop is mapped to X-dimension of both thread block and grid,

and y-loop is mapped to Y-dimension of both thread block and grid.

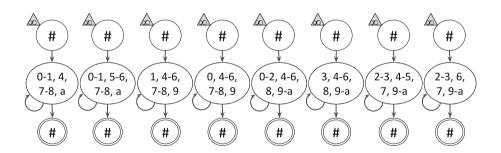

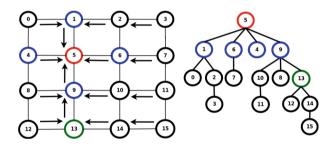

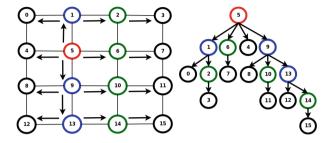

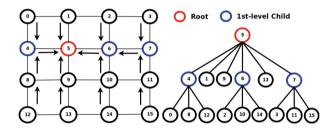

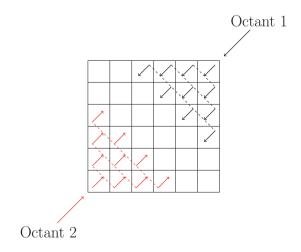

These loop schedule directives are implicitly added by the compiler. The graphical explanation for these loop schedules are shown in Figs. 2, 3 and 4. The detailed mapping function from the loop iterations to GPU threads for double nested loop are shown in Listings 1.3, 1.4 and 1.5. The purpose of schedule 2.2 is to overcome the GPU hardware threads limit within a block. In both schedule 2.1 and 2.2, the threads computing the outer loop are in different thread blocks, which are likely to be scheduled to different GPU SMs (Streaming Multiprocessor). This may not exploit the data locality efficiently. So how do we improve data locality? We consider the loop schedule 2.3 that allows some threads computing the outer loop iterations to remain in the same block thus improving data locality. For triple nested loop, a code example is shown in Listing 1.2 and other similar loop schedules are designed. Because of the space limit, we only illustrate the graphical representation for one loop schedule in Fig. 5, in which x-loop, yloop and z-loop refer to the inner most loop, the middle loop and the outer most loop, respectively. The loop schedule in Fig. 5 means x-loop is mapped to X-dimension of thread block, y-loop is mapped to Y-dimension of thread block and z-loop is mapped to X-dimension of the grid.

```

#pragma acc loop  \begin{cases} \text{for} (\mathbf{j} = j_{start}; \ \mathbf{j} < j_{end}; \ \mathbf{j} + +) \{ \\ \text{#pragma acc loop} \\ \text{for} (\mathbf{i} = i_{start}; \ \mathbf{i} < i_{end}; \ \mathbf{i} + +) \{ \\ \dots \\ \} \\ \end{cases}

```

**Listing 1.1.** Double nested loop example

```

#pragma acc loop for (k = k_{start}; k < k_{end}; k++) {

#pragma acc loop for (j = j_{start}; j < j_{end}; j++) {

#pragma acc loop for (i = i_{start}; i < i_{end}; i++) {

.....}

}

```

**Listing 1.2.** Triple nested loop example

Listing 1.3. Loop schedule 2\_1

Listing 1.4. Loop schedule 2\_2

**Listing 1.5.** Loop schedule 2\_3

Fig. 2. Loop schedule 2\_1

Fig. 3. Loop schedule 2\_2

Fig. 4. Loop schedule 2\_3

Fig. 5. Loop schedule 3\_1

## 4.3 Thread Scheduling

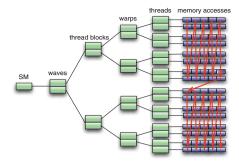

The memory trace is defined for how the memory is accessed by threads, which is further defined for how the thread blocks are scheduled into different SMs and how the threads are scheduled within each SM. When the GPU launches a grid of threads for a kernel, that grid is divided into 'waves' of thread blocks. For example let us assume there are 15 SMs. Each SM has 2 thread blocks hence 30 thread blocks in total. Thread block 0 and thread block 15 will be assigned to SM0. Thread block 1 and thread block 16 will be assigned to SM1. If there was a scenario with 60 thread blocks and each SM allows at most 2 blocks (30 blocks for 15 SMs), we will need to assign these blocks into two waves; 30 thread blocks to the first wave and the other 30 thread blocks to the second wave. We use round-robin scheduling mechanism to schedule the thread blocks to all SMs in all waves. The number of threads scheduled is independent of the grid size. For instance, if the grid size is 2048 and only 128 threads are scheduled, then each thread will process 2048/128=16 elements.

Figure 6 shows thread scheduling mechanism. It highlights two waves scheduled to one SM. Each wave has two thread blocks; each thread block has two warps; each warp has two threads; each thread has five memory accesses. We access the memory references in a round-robin manner. This memory access pattern gives us the memory trace.

The equation to calculate the number of waves is given in Eq. 1. The number of waves is obtained by dividing the total number of thread blocks by the active thread blocks per SM times the number of SMs. The active blocks per SM is given in Eq. 2. For instance, in Kepler GPU, the <code>max\_threads\_per\_SM</code> is 2048 and <code>max\_thread\_blocks\_per\_SM</code> is 16 and upon knowing the number of thread blocks in the kernel, which is specified by the launch configuration, we can determine the number of waves.

$$waves = \frac{thread\_blocks}{active\_blocks\_per\_SM \times \#SMs}$$

(1)

Fig. 6. Thread scheduling used in the auto-tuning framework

$active\_blocks\_per\_SM = min(max\_threads\_per\_SM/block\_size, max\_thread\_blocks\_per\_SM)$  (2)

# 4.4 Memory Access Cost Model

After memory coalescing, the memory trace is fed into the memory access cost model which computes the memory access cost for a specific loop schedule and launch configuration. The metric used in this model is presented as

$$Cost_{mem} = \sum_{i}^{\#levels} (N_i \times L_i)$$

(3)

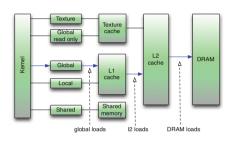

where  $N_i$  means the number of transactions happened in level i of the memory hierarchy, and  $L_i$  means the latency of memory level i.

The rationale behind this metric is the memory hierarchy in GPU architecture which is shown in Fig. 7. When the kernel needs to access a global memory address, it needs to load that address from L1 cache. If the data is already in L1 cache, then the access is a hit. If the data is not in L1 cache, then the access is a miss and it needs to load the data from L2 cache. If the data is not in L2 cache, then it needs to further load the data from DRAM. So the formula after expanding the Eq. 3 is shown in Eq. 4, which is the sum of memory access cost from L1, L2 and DRAM. The formula for calculating each individual cost is given in Eqs. 5, 6 and 7. The '4' in Eqs. 6 and 7 explains the number of global memory load transaction that is increased by 1 every 128 bytes in L1 cache, but every 32 bytes in L2 cache and DRAM. Since the memory access latency order from high to low - DRAM, L2 cache and L1 cache, we would like to access higher order memory as less as possible. In other words, we would like to have few global loads and low L1 and L2 cache miss rates as possible. When there is intra-thread data reuse or inter-thread data reuse, different loop schedules have

different cache miss rates, and finally the performance of the kernels using those loop schedules would be different.

$$Cost_{mem} = Mem_{L1} + Mem_{L2} + Mem_{DRAM}$$

(4)

$$Mem_{L1} = global\_loads * (1 - L1\_miss\_rate) * L1\_latency$$

(5)

$$Mem_{L2} = global\_loads * L1\_miss\_rate * 4 * L2\_latency$$

(6)

$Mem_{DRAM} = global\_loads * L1\_miss\_rate * L2\_miss\_rate * 4 * DRAM\_latency$  (7)

Fig. 7. GPU memory hierarchy

Fig. 8. L1 cache modeling

The key factors of the model are to estimate the global memory loads, L1 and L2 cache miss rates. To estimate L1 and L2 cache miss rate, we use reuse distance model [4]. It is a classic model to model the cache misses in CPU applications. The primary reasons for cache misses are cold/compulsory, conflict, capacity misses, famously termed as the 3 C model. The **cold miss** occurs when there is no data in the cache, no matter how big the cache is. The **conflict miss** usually occurs in direct-mapped caches and set-associative caches. Two cache lines may map to the same cache slot even though there may be empty slots. The **capacity miss** happens when there are no more available slots in the cache. The reuse distance model assumes that a LRU replacement fully associative cache is used. So it can only predict cold miss and capacity miss.

To the best of our knowledge, there is no existing work that discusses GPU L2 cache modeling. We found a couple of other related research work discussing GPU L1 cache modeling. Tang et al. [17] applied the reuse distance theory to model the GPU L1 cache. However, there were a few weaknesses and limitations in their approach: (1) they assumed only one thread block is active in one SM which is not true in the real hardware; (2) they modeled the cold miss and conflict miss but did not model capacity miss, however some research have shown that only a minority of the misses are conflict misses in both CPU [6] and GPU [14]; (3) they validated their model against a GPU simulator which is not a real hardware per se. Nugteren et al. [14] also used the reuse distance to model GPU L1 cache. However, in their implementation, all thread blocks were scheduled into

only one SM which is not the case in a real hardware. Our thread scheduling mechanism overcomes the drawbacks of the above two papers discussed.

The reuse distance theory can measure both spatial locality and temporal locality if the distance is measured with cache line granularity. The spatial locality defines that the nearby memory addresses are likely to be referenced again in the near future. The temporal locality defines that the same data is likely to be referenced again in the near future.

The spatial locality is reflected by the memory coalescing level in the GPU kernel. If a GPU kernel has coalesced memory accesses, then it has better spatial locality than the kernel that has uncoalesced memory accesses. This is because the coalesced memory accesses allow the nearby data elements to be accessed at the same time the current data is accessed.

The temporal locality is reflected by the loop schedule. Different loop schedules pose different temporal locality since the execution order of the threads are different. The reuse distance theory can capture both the spatial locality and temporal locality effectively. Table 2 shows a reuse distance example. In this example, assume the cache line is of 16 bytes. If the data is accessed first or when a cold miss happens, the reuse distance is recorded as  $\infty$ . The reuse distance is a metric that defines the *distinct* memory accesses between the current memory access and the last access. If the reuse distance is larger or equal to the total number of cache lines, then a data reference is missed in the cache. The cache hit rate can be obtained by diving the hits by the total number of hits and misses.

**Table 2.** Reuse distance example. Assume cache line has 16 bytes and the cache size is 32 bytes. The reuse distance is based on cache line granularity

| Address        | 0        | 8   | 16       | 96       | 8    | 16   | 17  | 104  |

|----------------|----------|-----|----------|----------|------|------|-----|------|

| Cache line     | 0        | 0   | 1        | 6        | 0    | 1    | 1   | 6    |

| Reuse distance | $\infty$ | 0   | $\infty$ | $\infty$ | 2    | 2    | 0   | 2    |

| Cache hit/miss | Miss     | Hit | Miss     | Miss     | Miss | Miss | Hit | Miss |

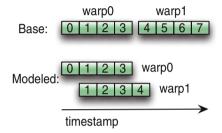

Although the classic reuse distance model can predict the cache miss rate in CPU, it cannot be simply applied as-is on the GPU since the architectures are significantly different. The most important difference is that in GPU, the threads in a warp execute in lock-step manner and therefore memory coalescing is important in the memory accesses of a warp. If the memory addresses referenced by all the threads in a warp are in a cache line, then the memory accesses are merged into one memory access. Another difference is the parallel processing feature including parallel memory processing in GPU. Therefore in our implementation, the L1 modeling includes parallel memory processing. But we also compare it with the base implementation. The difference of "Base" and "Modeled" are shown in Fig. 8. In Base version, the memory coalescing is applied to the memory trace. Then the memory requests from different warps are processed in order. If the memory requests in a warp are not coalesced, then

they are also processed in order within a warp. In Modeled version, we also apply memory coalescing, but we further add a timestamp. The timestamp is added to the following warps but it is also added to the threads in the same warp if their memory requests are not coalesced.

In the reuse distance model implementation, a key factor is the input, which is a memory trace. In our analytical model, the memory traces are different for different loop schedules. This is because different loop schedules assign the loop iterations into GPU threads differently, therefore the memory traces are different, and eventually the cache misses are different.

For L2 cache modeling, we must first apply L1 cache modeling for all SMs and record the cache misses in their individual list. Then the memory trace is processed in round-robin manner which is similar to the description in Fig. 6.

# 5 Performance Evaluation

The experimental platform is Intel Xeon processor E5520 with frequency 2.27 GHz and 32 GB main memory and an Nvidia Quadro K6000 GPU card which uses K40 architecture. L1 and L2 cache sizes are 16 KB and 1.5 MB, respectively. The cache line size for both L1 and L2 is 128 bytes. The proposed framework is implemented within the OpenUH compiler. The actual L1 and L2 cache hit rates are obtained from l1\_cache\_global\_hit\_rate and l2\_l1\_read\_hit\_rate metrics in CUDA profiler nvprof and the actual global memory loads are obtained from gld\_transactions metric.

To evaluate our auto-tuning framework, we consider several benchmarks: two synthetic benchmarks (x-reuse and y-reuse), four from kernelGen OpenACC Performance Test Suite [2] (Matrix Multiplication, Jacobi, Laplacian and Divergence), one from CUDA SDK (Matrix Transpose) and one from EPCC OpenACC benchmarks [1] (Himeno). We test different data reuse patterns using the two synthetic benchmarks. Figure 9 shows these two benchmarks along with another pattern i.e. xy-reuse, a classic Matrix Multiplication case. The "x" here refers to the inner loop and "y" refers to the outer loop in a double nested loop. In the x-reuse benchmark, the inner loop reuses the common data; while in the y-reuse benchmark, the outer loop reuses the common data. The third case is the xy-reuse where both the inner and the outer loop reuse some common data.

Fig. 9. Data reuse patterns

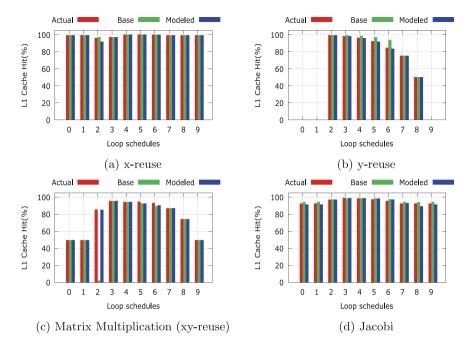

Figure 10 shows results for L1 cache hit modeling for some of the benchmarks discussed above. Figure 10(a) and (b) are results for the two synthetic benchmarks and Fig. 10(c) and (d) are results for a couple of benchmarks from kernelGen suite. (Results for other benchmarks were quite similar, so due to space constraints we have not included them in the paper). The results indicate that modeled result is more accurate than "Base" version since it considers the parallel memory processing. Figure 10(a) shows that cache hit rates are high for all loop schedules. This is because for all iterations in x loop, the data they share are in one row and in the same contiguous memory section. Figure 10(b) shows that the shared data are in the same column and therefore they are not contiguous in memory. This leads to relatively lower cache hit. Figure 10(c), results for Matrix Multiplication, show that there is data reuse in both x and y loops and therefore the shape of cache hit results seem like a combination of x-reuse and y-reuse. Figure 10(d), results for Jacobi show that, the overall hit rate is slightly lesser than x-reuse. This is because the data, the threads share are stencil-like. For instance considering a 4-point stencil, for different points, the data that the threads access are not in contiguous memory locations, however for a specific point the data, the threads share, are still in contiguous memory location. As a result the cache hit rates are still relatively high. If the cache hit is high, the indication is that the threads will take lesser time to fetch data from high-latency memory.

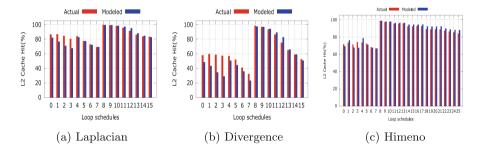

The GPU L2 cache modeling result is shown in Fig. 11. We show the results for partial benchmarks including Laplacian, Divergence and Himeno. The results indicate that some loop schedules have low L2 cache hit while other loop schedules have high L2 cache hit. This illustates the importance of choosing the right loop schedules. The error percentage between the actual and the modeled L2 hit is only 4.37%, 13.72% and 2.76% for Laplacian, Divergence and Himeno, respectively. The low error percentages indicate that our model can capture the L2 locality for different loop schedules accurately.

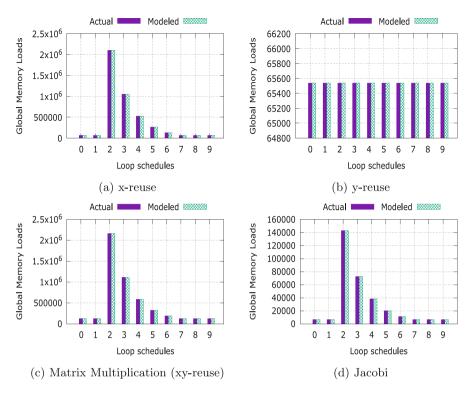

Figure 12 shows the global memory loads of kernels for the four benchmarks discussed in Fig. 10. The plots show that the modeled loads (before kernel launch) are exactly the same as the actual loads (profiled results) thus indicating that our proposed model is accurately predicting the memory loads. Figure 12(b) indicates that for y-reuse synthetic benchmark, no matter what the loop schedule is, the memory access appears to be fully coalesced leading to the same number of global memory loads all the time. In the other three plots, the tallest bars indicate the loop schedules for which the memory accesses are fully uncoalesced, while the shortest bars indicate the loop schedules for which memory accesses are fully coalesced, and the bars between the tallest and the shortest bars indicate partial memory coalescing. (Results for other benchmarks in kernelGen suite and EPCC were quite similar, so due to space constraints we have not included them in the paper). Higher the global memory loads, higher the time taken by the threads to process the memory requests.

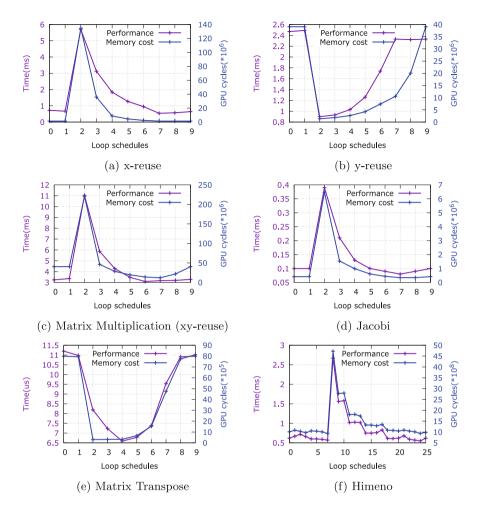

Figure 13 shows several plots that demonstrate close correlation of kernel performance and the memory access cost modeling. We use the coefficient of

Fig. 10. GPU L1 cache modeling (Color figure online)

Fig. 11. GPU L2 cache modeling (Color figure online)

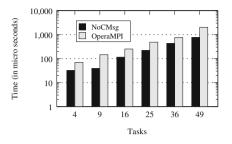

determination  $R^2$  to measure the strength of the relationship between the kernel performance and the memory access cost in the model.  $R^2$  is a popular indicator on how well a variable can be used to predict the value of another variable. The values of  $R^2$  range from 0 (poor indicator) to 1 (excellent predictor). The  $R^2$  value for all benchmarks are listed in Table 3 and the average value is 0.93 indicating the strong correlation between the kernel performance and the memory access cost modeling. Based on the memory access cost modeling, an optimal or a sub-optimal loop schedule is chosen by the framework. For all benchmarks tested, the speedup of the loop schedule chosen by the model against the default loop

Fig. 12. Global memory loads (Color figure online)

schedule chosen by the compiler are listed in Table 3 and the average speedup is 1.29x. This proves the effectiveness of the proposed framework.

# 6 Related Work

To the best of our knowledge, there were only a few similar research on how to solve the loop scheduling issues on a GPU. Siddiqui et al. [16] presented how to choose the optimal loop schedule with machine learning approach. They used exhaustive search to find the optimal and sub-optimal loop schedules for the training data sets and stored those information into a database. For the new test benchmark, they found the closest training benchmark and applied its loop schedules to that test benchmark. Their approach, however, could only be used for different problem sizes in the same application because it was difficult to define how close two applications are. Instead of exhaustive search, Montgomery et al. [13] used more efficient search approach such as direct search to find the optimal loop schedule. Their approach required to execute the kernels with different loop schedules. Our approach, however, only needs to run the kernel once on CPU because the model predicts the optimal loop schedule before the kernel's execution on GPU. This is one of the major highlights of our proposed framework.

Fig. 13. Plots demonstrating correlation of performance vs memory access cost modeling (Color figure online)

Table 3. Evaluation results

| Benchmark             | Source                 | Nested loop type | $R^2$ | Speedup |

|-----------------------|------------------------|------------------|-------|---------|

| x-reuse               | Synthetic              | Double           | 0.927 | 1.0     |

| y-reuse               | Synthetic              | Double           | 0.683 | 2.74    |

| Matrix multiplication | Performance test suite | Double           | 0.913 | 1.03    |

| Jacobi                | Performance test suite | Double           | 0.998 | 1.1     |

| Laplacian             | Performance test suite | Triple           | 0.999 | 1.05    |

| Divergence            | Performance test suite | Triple           | 0.999 | 0.96    |

| Matrix transpose      | CUDA SDK               | Double           | 0.943 | 1.37    |

| Himeno                | EPCC                   | Triple           | 0.994 | 1.09    |

Lee et al. [11] presented a framework to automatically and efficiently map a nested loop to GPU using Domain Specific Language (DSL). The parameters that form the search space included the dimension of the nested loop, the block size and degree of parallelism, which is essentially the grid size. They applied some hard constraints and soft constraints to restrict the search space. For all loop schedules we consider, many of them have the same software constraints such as the level of memory coalescing. The cache locality, which is a key factor, was not considered in their model.

We looked into some of the other related work on auto-tuning, [8,9,12]; these papers obtained the performance of auto-tuning the kernels by running those kernels. Our goal is different from them since we use an analytical model to predict the loop schedule without running the kernel. Hu et al. [10] and Baghsorkhi et al. [5] used analytical models to predict the performance of a kernel. Our work, however, do not need to predict the execution time of a kernel accurately because the computation part is the basically the same for all loop schedules and the difference of the performance part is the memory cost. Other research include the effect of cache on GPU applications. Picchi and Zhang [15] applied L2 cache locking mechanism to improve GPU application performance. Choi and Kim [7] analyzed the L1 and L2 cache behavior for some benchmarks with a GPU simulator.

# 7 Conclusion and Future Work

This paper discusses the importance of auto-tuning loop scheduling for GPU computing. We propose an analytical model-based auto-tuning framework to find the optimal or sub-optimal loop schedule that is better than the default loop schedule chosen by the compiler. The model used in the framework is locality-aware as it can predict the cache locality for each loop schedule. The model also predicts the total number of global memory loads and based on these information it obtains a memory access cost for each loop schedule. The framework iterates over all loop schedule patterns and launch configuration space and picks the loop schedule with the least memory access cost. We analyze the proposed framework with multiple benchmarks. The results indicate that the memory access cost modeling has strong correlation with the kernel performance and the loop schedule picked by the framework can achieve 1.29x speedup over the default loop schedule chosen by the compiler. For the future work, we will integrate more factors into the model to improve the prediction of the loop schedule that is as close as the optimal loop schedule.

# References

- 1. EPCC OpenACC Benchmarks (2015). https://www.epcc.ed.ac.uk/research/computing/performance-characterisation-and-benchmarking/epcc-openacc-benchmark-suite

- 2. KernelGen Performance Test Suite, December 2015. https://hpcforge.org/plugins/mediawiki/wiki/kernelgen/index.php/Performance\_Test\_Suite

- 3. OpenACC (2016). http://www.openacc.org

- Almási, G., Caşcaval, C., Padua, D.A.: Calculating stack distances efficiently. In: ACM SIGPLAN Notices, vol. 38, pp. 37–43. ACM (2002)

- Baghsorkhi, S.S., Delahaye, M., Gropp, W.D., Wen-mei, W.H..: Analytical performance prediction for evaluation and tuning of GPGPU applications. In: Workshop on EPHAM2009, in Conjunction with CGO, Citeseer (2009)

- Beyls, K., Hollander, E.D.: Reuse distance as a metric for cache behavior. In: Proceedings of the IASTED Conference on Parallel and Distributed Computing and Systems, vol. 14, pp. 350–360 (2001)

- Choi, K.H., Kim, S.W.: Study of cache performance on GPGPU. IEIE Trans. Smart Process. Comput. 4(2), 78–82 (2015)

- 8. Cui, X., Chen, Y., Zhang, C., Mei, H.: Auto-tuning dense matrix multiplication for GPGPU with cache. In: IEEE 16th International Conference on Parallel and Distributed Systems (ICPADS), pp. 237–242. IEEE (2010)

- Grauer-Gray, S., Xu, L., Searles, R., Ayalasomayajula, S., Cavazos, J.: Auto-tuning a high-level language targeted to GPU codes. In: Innovative Parallel Computing (InPar), pp. 1–10. IEEE (2012)

- Hu, Y., Koppelman, D.M., Brandt, S.R., Löffler, F.: Model-driven auto-tuning of stencil computations on GPUs. In: Proceedings of the 2nd International Workshop on High-Performance Stencil Computations, pp. 1–8 (2015)

- 11. Lee, H., Brown, K.J., Sujeeth, A.K., Rompf, T., Olukotun, K.: Locality-aware mapping of nested parallel patterns on GPUs. In: 47th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO), pp. 63–74. IEEE (2014)

- Mametjanov, A., Lowell, D., Ma, C.-C., Norris, B.: Autotuning stencil-based computations on GPUs. In: IEEE International Conference on Cluster Computing (CLUSTER), pp. 266–274. IEEE (2012)

- Montgomery, C., Overbey, J.L., Li, X.: Autotuning openACC work distribution via direct search. In: Proceedings of the 2015 XSEDE Conference: Scientific Advancements Enabled by Enhanced Cyberinfrastructure, p. 38. ACM (2015)

- Nugteren, C., van den Braak, G.-J., Corporaal, H., Bal, H.: A detailed GPU cache model based on reuse distance theory. In: High Performance Computer Architecture (HPCA), pp. 37–48. IEEE (2014)

- 15. Picchi, J., Zhang, W.: Impact of L2 cache locking on GPU performance. In: SoutheastCon, pp. 1–4. IEEE (2015)

- Siddiqui, S., AlZayer, F., Feki, S.: Historic learning approach for auto-tuning openACC accelerated scientific applications. VECPAR-2014. LNCS, vol. 8969, pp. 224–235. Springer, Heidelberg (2014)

- 17. Tang, T., Yang, X., Lin, Y.: Cache miss analysis for GPU programs based on stack distance profile. In: 31st International Conference on Distributed Computing Systems (ICDCS), pp. 623–634. IEEE (2011)

- Tian, X., Xu, R., Yan, Y., Yun, Z., Chandrasekaran, S., Chapman, B.: Compiling a high-level directive-based programming model for GPGPUs. LCPC 2013. LNCS, vol. 8664, pp. 105–120. Springer International Publishing, New York (2014)

# Performance, Design, and Autotuning of Batched GEMM for GPUs

Ahmad Abdelfattah<sup>1(⊠)</sup>, Azzam Haidar<sup>1</sup>, Stanimire Tomov<sup>1</sup>, and Jack Dongarra<sup>1,2,3</sup>

Department of Electrical Engineering and Computer Science, University of Tennessee, Knoxville, USA {aahmad2,haidar,tomov,dongarra}@eecs.utk.edu

Oak Ridge National Laboratory, Oak Ridge, USA

University of Manchester, Manchester, UK

Abstract. The general matrix-matrix multiplication (GEMM) is the most important numerical kernel in dense linear algebra, and is the key component for obtaining high performance in most LAPACK routines. As batched computations on relatively small problems continue to gain interest in many scientific applications, a need arises for a high performance GEMM kernel for batches of small matrices. Such a kernel should be well designed and tuned to handle small sizes, and to maintain high performance for realistic test cases found in the higher level LAPACK routines, and scientific computing applications in general.

This paper presents a high performance batched GEMM kernel on Graphics Processing Units (GPUs). We address batched problems with both fixed and variable sizes, and show that specialized GEMM designs and a comprehensive autotuning process are needed to handle problems of small sizes. For most performance tests reported in this paper, the proposed kernels outperform state-of-the-art approaches using a K40c GPU.

**Keywords:** GEMM  $\cdot$  Batched GEMM  $\cdot$  HPC  $\cdot$  GPU computing  $\cdot$  Autotuning

# 1 Introduction

Scientific computing applications extract their high-performance (HP) and efficiency through fast linear algebra libraries, and most notably the GEMM routine. Indeed, in the area of dense linear algebra (DLA), algorithms are designed as much as possible to use GEMM, e.g., as in the LAPACK library. For example, direct solvers for large dense linear system and least squares problems require  $O(n^3)$  floating point operations (flops), of which  $O(n^3)$  are in GEMM. Consequently, they run as fast/efficiently as running GEMM. Application areas that rely on DLA, and therefore GEMM, are computational electromagnetics, material science, fluid dynamics, applications using boundary integral equations, computational statistics, econometrics, control theory, signal processing, curve fitting, and many more. Therefore, even a slight improvement in GEMM, is extremely valuable and has great impact.

© Springer International Publishing Switzerland 2016 J.M. Kunkel et al. (Eds.): ISC High Performance 2016, LNCS 9697, pp. 21–38, 2016. DOI: 10.1007/978-3-319-41321-1\_2

Aside from scientific computing that requires large DLA, numerous other applications, that will normally require sparse linear algebra computations, use domain decomposition type frameworks where the overall computation is cast in terms of many, but small enough, problems/tasks to fit into certain levels of the machines' memory hierarchy. Many times it is advantageous to represent these small tasks as DLA problems on small matrices, as in applications such as astrophysics [16], metabolic networks [11], CFD and the resulting PDEs through direct and multifrontal solvers [22], high-order FEM schemes for hydrodynamics [5], direct-iterative preconditioned solvers [9], and some image [17] and signal processing [3]. Moreover, even in the area of DLA itself, large dense matrices can be broken into tiles and the algorithms expressed in terms of small tasks over them [2]. Also note that, implementation-wise, large GEMMs are parallelized on current computing architectures, including GPUs, as many small GEMMs. Under these circumstances, the only way to achieve good performance is to find a way to group these small inputs together and run them in large "batches." The most needed and performance-critical kernel here is a batched GEMM [4,7.8]. Finally, tensor contractions, used to model multilinear relations in areas of recent interest like big-data analytics and machine learning, as well as large scale highorder FEM simulations, can also be reduced to batched GEMMs [1].

To address the needs for batched linear algebra on new architectures, as outlined above, we designed high-performance batched GEMM algorithms for GPUs. We consider batched problems with both fixed and variable sizes. While we leverage optimization techniques from the classic GEMM kernel for one multiplication at a time, we also developed a different design scheme for the tuning process that can flexibly select the best performing set of tuning parameters. For variable size problems, we propose new interfaces, as well as techniques, to address the irregularity of the computation. We show that aside from the performance critical algorithmic designs and innovations, a comprehensive autotuning process is needed in order to handle the enormous complexity of tuning all GEMM variants resulting from our designs. The complexity is further exacerbated by targeting problems for entire ranges of small sizes (vs. for a few discrete sizes). Using a K40c GPU, the proposed kernels outperform state-of-the-art approaches (e.g., cuBLAS and MKL libraries) in most of the performance tests reported in this work.

# 2 Related Work

To enable GPUs for a large-scale adoption in the HP scientific computing arena, a fast GEMM had to be developed. This became feasible with the introduction of shared memory in the GPUs. While general purpose GPU computing was possible before that, performance was memory bound, as data - once read - could not be reused in many computations. The availability of shared memory made data reuse possible, and the first compute-bound GEMM for GPUs was developed in 2008 [21]. As the GPUs continued improving, new GEMM algorithms had to be developed to better use to the evolving architecture, especially its memory

hierarchy. In particular, [18] presented a GEMM algorithm and implementation (in MAGMA, later incorporated in cuBLAS) that applied hierarchical communications/blocking on all memory levels available at the time, including a new register blocking. Blocking sizes, along with other performance-critical choices were parametrized and used in autotuning frameworks [12,14], but improvements were limited to certain very specific matrix sizes. Coding these multilevel blocking types of algorithms in native machine language was used to overcome some limitations of the CUDA compiler or warp scheduler (or both) to achieve better performance [19]. Similarly, assembly implementations [6,13] are used today in cuBLAS for Kepler and Maxwell GPUs to obtain higher performance than corresponding CUDA codes.

Besides the batched GEMM in cuBLAS, there have been a number of research papers on batched GEMM, developed as needed for particular applications. For example, a batched GEMM for very small sizes (up to 16) was developed for a high-order finite element method (FEM) [10]. Tensor contraction computations for large scale high-order FEM simulations were reduced to batched GEMM [1], obtaining close to peak performance for very small matrices (90+% of a theoretically derived peak) using some of the techniques that we developed and describe in detail here. Matrix exponentiation from the phylogenetics domain was reduced to batched GEMMs on small square matrices [15], obtaining very good performance for fixed sizes (4, 20, and 60) in single precision.

# 3 Batched GEMM Design and Implementation Details

This section discusses the main design and tuning approaches for batched GEMM kernels that support both fixed and variable sizes. From now on, variable size batched GEMM is abbreviated as *vbatched* GEMM. Our goal is to minimize coding effort and to design one kernel that could be easily adapted for use in both fixed and variable size batched GEMM. We begin by considering only fixed size batched problems. We then discuss the modifications we incorporated to handle a variable size problem at the end of the section.

**Routine Interface.** Each GEMM in a batch routine has the form of the standard BLAS GEMM:

$$C = \alpha \cdot op(A) \times op(B) + \beta \cdot C$$

where A, B, and C are matrices,  $\alpha$  and  $\beta$  are input scalars, and op() specifies whether an input matrix is transposed. The interface of a batched/vbatched kernel must manage independent multiplications of matrices that are not necessarily stored contiguously in memory. As a result, the batched kernel requires the address of every individual matrix. It also requires the size and the leading dimension of every matrix. While such information can be passed using single integers in the fixed sizes case, arrays of integers are needed for the vbatched problems. Our kernels support multiplications with different values for  $\alpha$  and  $\beta$ . We also add an extra input argument batchCount that indicates the number of matrices in the batch. Table 1 summarizes an example of the interface written in the C language for the batched/vbatched DGEMM routine.

**Table 1.** Interface of batched and vbatched matrix multiplication kernel against standard BLAS interface (GEMM:  $C = \alpha \cdot op(A) \times op(B) + \beta \cdot C$ ).

| Argument   | Description                         | BLAS    | Batched  | Vbatched |

|------------|-------------------------------------|---------|----------|----------|

| TRANSA     | op(A)                               | char    | char     | char     |

| TRANSB     | op(B)                               | char    | char     | char     |

| М          | Rows of $op(A)/C$                   | int     | int      | int*     |

| N          | Columns of $op(B)/C$                | int     | int      | int*     |

| K          | Columns of $op(A)$ /rows of $op(B)$ | int     | int      | int*     |

| α          | Alpha                               | double  | double*  | double*  |

| A          | Input matrix                        | double* | double** | double** |

| LDA        | Leading dimension of A              | int     | int      | int*     |

| В          | Input matrix                        | double* | double** | double** |

| LDB        | Leading dimension of B              | int     | int      | int*     |

| β          | Beta                                | double  | double*  | double*  |

| С          | Input/output matrix                 | double* | double** | double** |

| LDC        | Leading dimension of C              | int     | int      | int*     |

| batchCount | Number of matrices                  | N/A     | int      | int      |

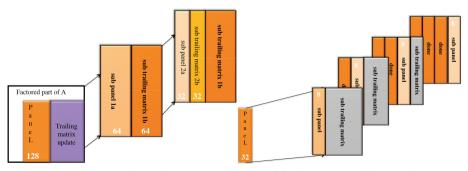

Fig. 1. Example of blocking in the GEMM kernel.

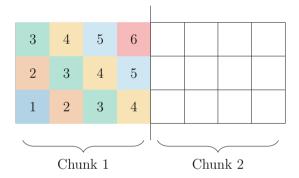

**Kernel Design.** To design a GEMM kernel in CUDA and take advantage of the available threads, thread blocks and multiprocessors of a GPU, the computation must be partitioned into blocks of threads (also called thread blocks, or simply TBs) that execute independently from each other on the GPU multiprocessors. To do that, as shown in Fig. 1, the matrix C can be subdivided into rectangular blocks of size  $BLK_M \times BLK_N$ , and each of these blocks computed by one TB.

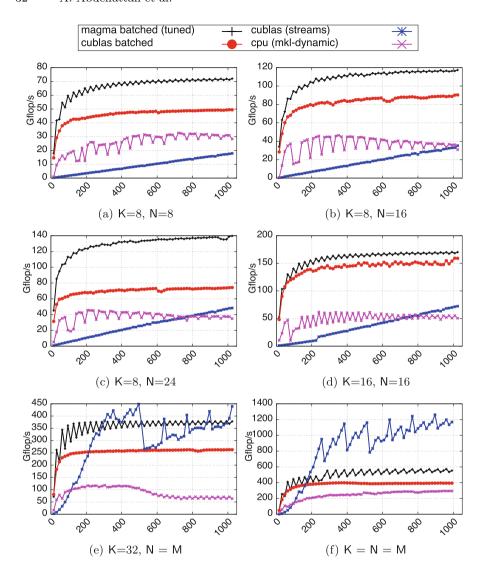

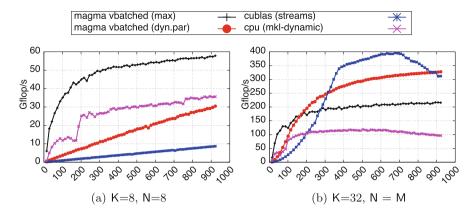

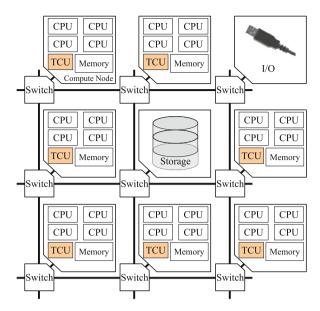

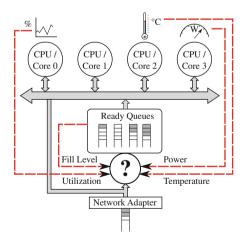

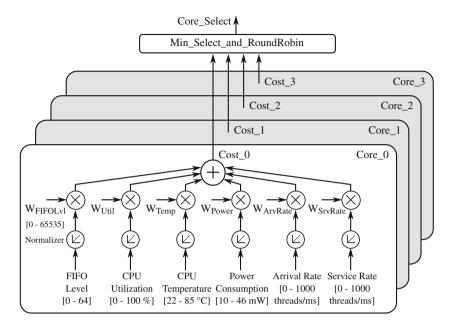

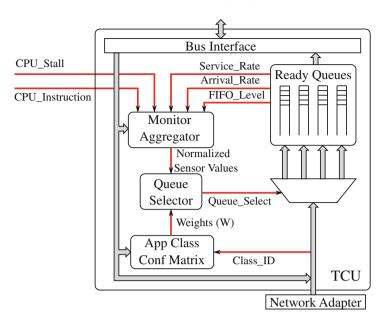

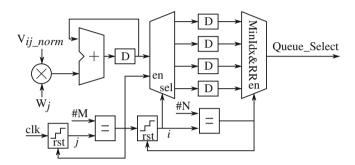

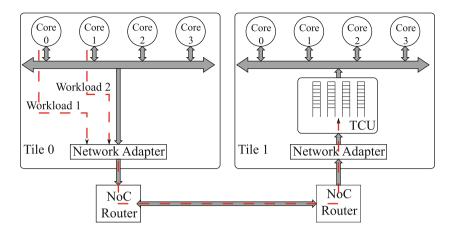

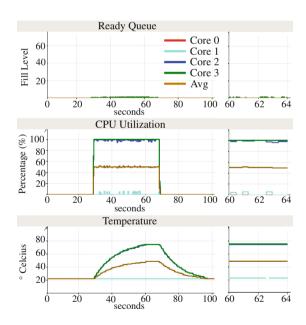

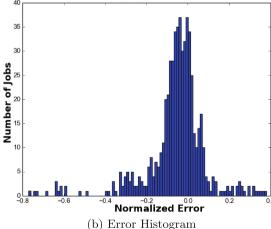

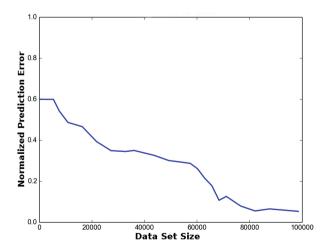

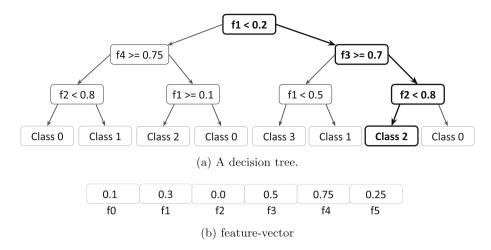

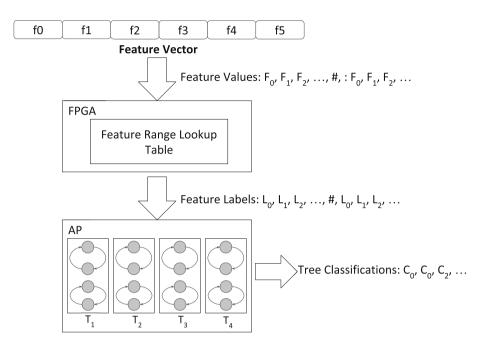

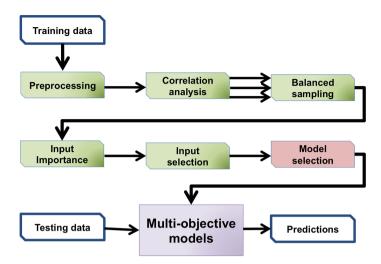

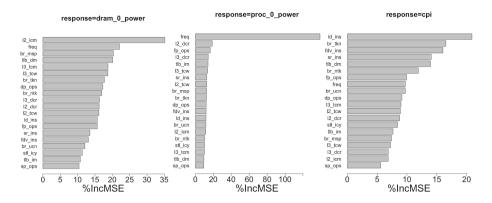

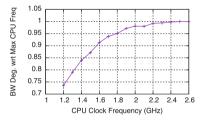

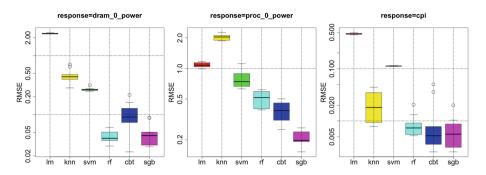

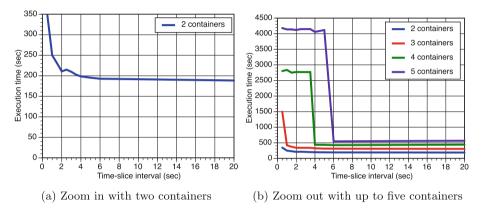

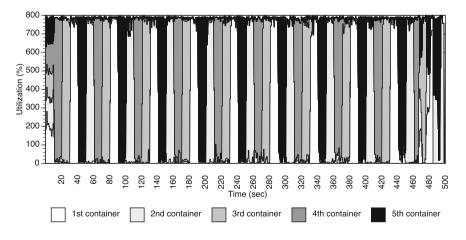

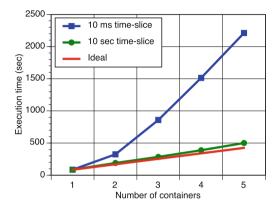

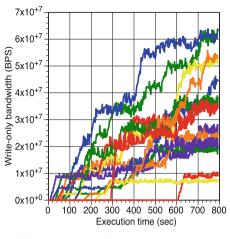

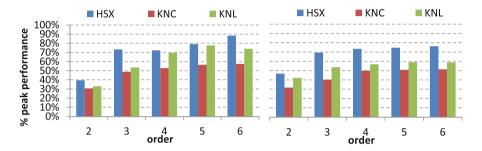

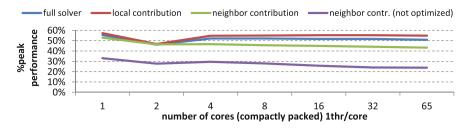

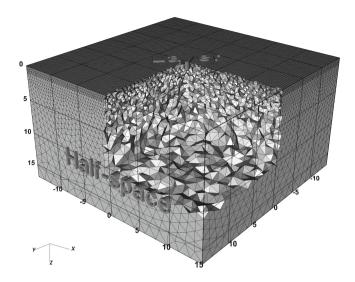

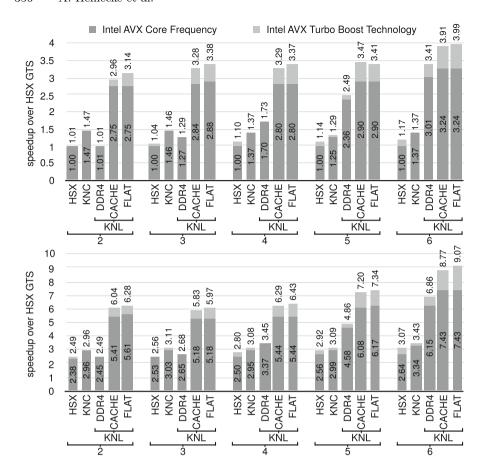

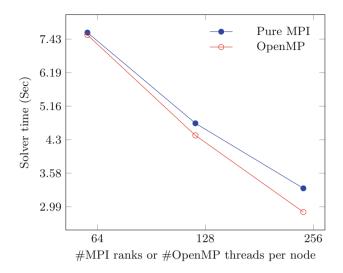

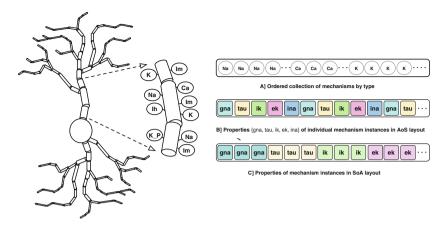

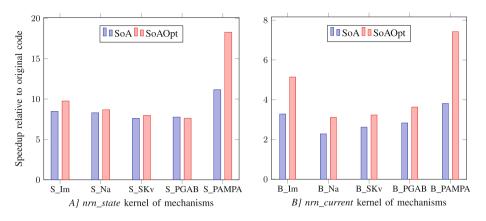

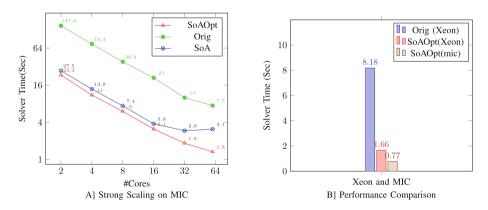

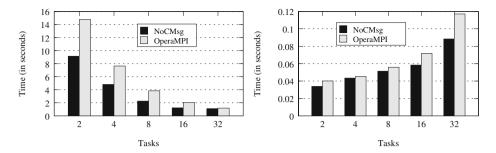

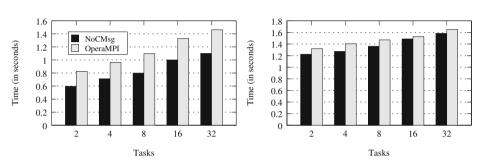

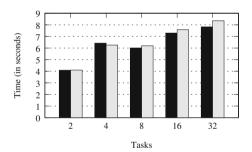

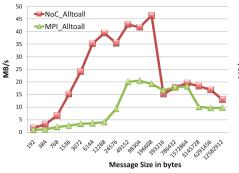

Specifics on how to do this efficiently, e.g., using hierarchical blocking of both communications and computations, as noted in Sect. 2, are given in a design by Nath et al. [18], which is also available in the MAGMA library [20]. We use these ideas to build an extended CUDA kernel that is efficient for batched computations (note that the batched GEMM in cuBLAS also uses this early MAGMA GEMM kernel). However, some rules change here in the case of small matrices. For example, the standard GEMM kernel design tries to maximize the use of shared memory while for batched small GEMM, we should minimize the use of shared memory to allow more than one TB to be executed on the same multiprocessor. The results obtained by our autotuning framework, described below, prove this choice.